- 您现在的位置:买卖IC网 > Sheet目录1996 > HMC700LP4E (Hittite Microwave Corporation)IC FRACT-N PLL 16BIT 24QFN

For price, delivery and to place orders: Hittite Microwave Corporation, 2 Elizabeth Drive, Chelmsford, MA 01824

978-250-3343 tel 978-250-3373 fax Order On-line at www.hittite.com

Application Support: apps@hittite.com

P

LL

-

F

r

a

c

t

io

n

a

L-

n

-

S

M

t

0

0 - 24

HMC700LP4 / 700LP4E

v11.0411

8 GHz 16-Bit Fractional-N PLL

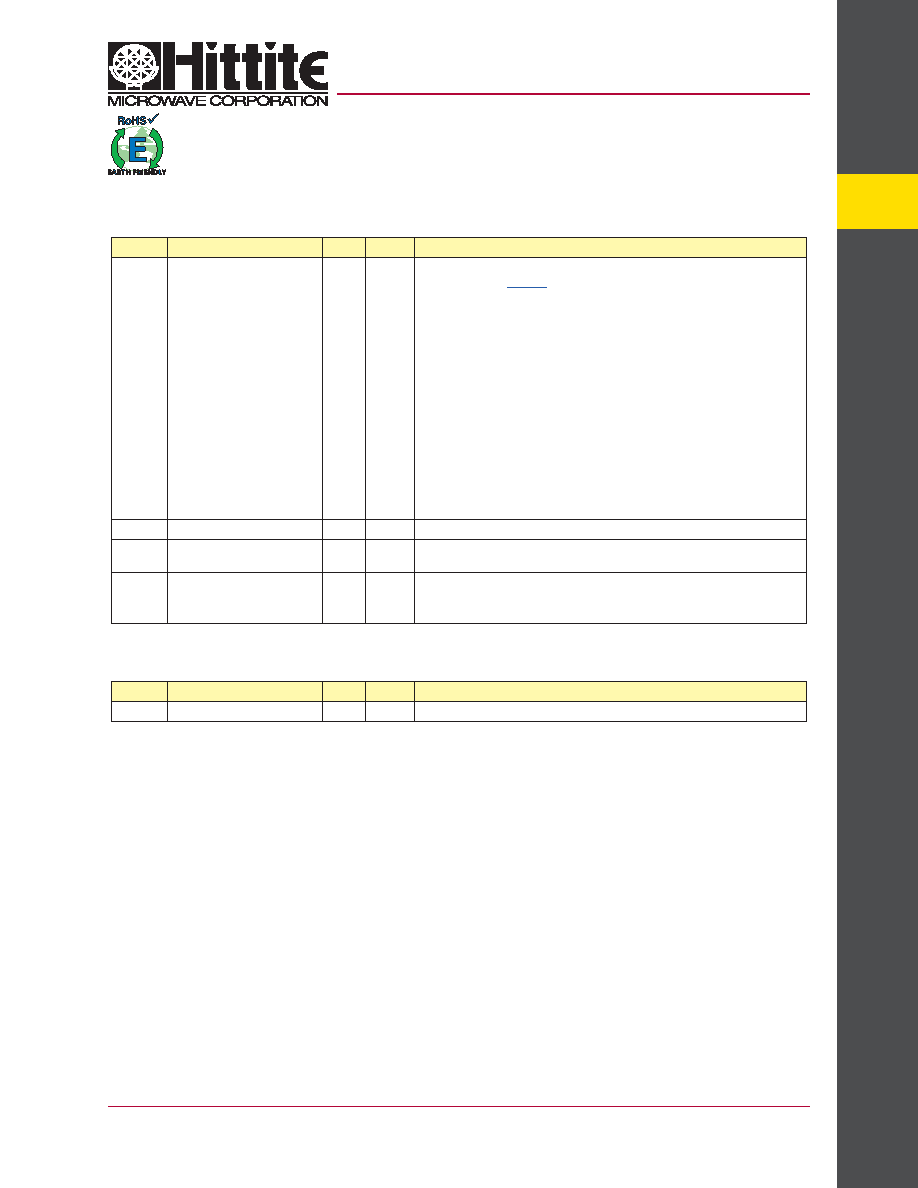

Table 20. Reg 0Dh GPO_SPI_RDIV Register

Bit

name

Width

Default

Description

[3:0]

gpo_select

4

10d

test signals selected here are output to gpo pins when

gpo_pads_en=1 (table 15)

D1 & D0

0: clk_vcodiv & clk_refdiv

1: pfd_up & pfd_dn

2: refout & refDivout

3: seed_stb_sypulse_test & frac_stb_sypulse_test

4: intg_inbuff_enable_test & clk_sd

5: oneshot_trigg_test & oneshot_pulse_test

6: ‘0’ & ringosc_test

7: csp_corr_add & csp_corr_sub

8: pfd_sat_refdiv & pfd_sat_vcodiv

9: (csp_corr_add or csp_corr_sub) & pfd_sat_rstb

10: gpo_test , see reg0D<5:4>

11: not used

12: not used

13: not used

14: not used

15: not used

[5:4]

gpo_test

2

0

data written to this register is output to D0 and D1 pins when gpo_select = 10d

[6]

refclkdiv4

1

0

1: sel ref divby4 for clocking the vco_spi

0: sel ref divby1 for clocking the vco_spi

[7]

to_gpo_sdo

1

0

enable the automatic output of vcospi_vco_data to LD_SDo

output Vco_SPi clock to D1 (see Reg0D<6>)

output Vco_SPi En to D0

Table 21. Reg 0Fh LD State Register (Read Only)

Bit

name

Width

Default

Description

[0]

locked

1

0

read only Lock Detect flag, 1 when locked

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HMC703LP4E

IC FRACT-N PLL W/SWEEPR 24QFN

HMC704LP4E

IC FRACT-N PLL 16BIT 24QFN

HMC830LP6GE

IC FRACT-N PLL W/VCO 40QFN

HMP8117CNZ

IC VIDEO DECODER NTSC/PAL 80PQFP

HMP8156ACNZ

IC VIDEO ENCODER NTSC/PAL 64MQFP

HSP45102SC-40Z

IC OSC NCO 40MHZ 28-SOIC

HSP45106JC-33Z

IC OSC NCO 33MHZ 84-PLCC

HSP45116AVC-52Z

IC OSC NCO 52MHZ 160-MQFP

相关代理商/技术参数

HMC700LP4ETR

制造商:Hittite Microwave Corp 功能描述:IC FRACT-N PLL 16BIT 24QFN 制造商:Hittite Microwave Corp 功能描述:HMC700 Series 8 GHz 16-Bit Prescaler Fractional-N PLL - 4x4 mm QFN-24

HMC701LP6C

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:8 GHz 16-BIT FRACTIONAL-N SYNTHESIZER

HMC701LP6C_10

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:8 GHz 16-BIT FRACTIONAL-N SYNTHESIZER

HMC701LP6CE

制造商:Hittite Microwave Corp 功能描述:IC SYNTHESIZER W/SWEEPER 40-QFN

HMC702LP6CE

制造商:Hittite Microwave Corp 功能描述:IC SYNTHESIZER W/SWEEPER 40-QFN

HMC702LP6CE_10

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:14 GHz 16-BIT FRACTIONAL-N SYNTHESIZER

HMC702LP6CE_11

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:14 GHz 16-BIT FRACTIONAL-N PLL

HMC703LP4E

功能描述:IC FRACT-N PLL W/SWEEPR 24QFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR